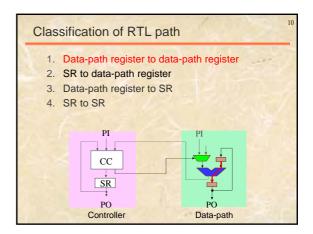

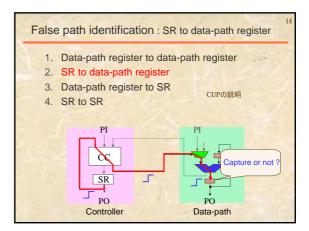

| False pa                                         | ath id | entif | ication : SR to data-path register |  |  |  |  |

|--------------------------------------------------|--------|-------|------------------------------------|--|--|--|--|

| SR loads a new value every clock                 |        |       |                                    |  |  |  |  |

| Idea: Consider transitions for each FF in the SR |        |       |                                    |  |  |  |  |

|                                                  |        |       |                                    |  |  |  |  |

| State                                            | assign | ment  | SR                                 |  |  |  |  |

|                                                  | FF0    | FF1   | FF0 FF1                            |  |  |  |  |

| SO                                               | 0      | 0     | (S1 S2) _ +                        |  |  |  |  |

| S1                                               | 0      | 1     |                                    |  |  |  |  |

| S2                                               |        | 1     | Load or Hold at S3 ?               |  |  |  |  |

| S3                                               | 1      | 0     |                                    |  |  |  |  |

| Data-path register                               |        |       |                                    |  |  |  |  |

| Experiments                                                                                                                  |         |                |        |             |        |          |       |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------|---------|----------------|--------|-------------|--------|----------|-------|--|--|--|

| The number of RTL path identified as a control dependent untestable path                                                     |         |                |        |             |        |          |       |  |  |  |

|                                                                                                                              |         | D_reg to D_reg |        | SR to D_reg |        | SR to SR |       |  |  |  |

| 1                                                                                                                            | Circuit | # CUPs         | Ratio  | # CUPs      | Ratio  | # CUPs   | Ratio |  |  |  |

|                                                                                                                              | Paulin  | 12 (29)        | 41.4 % | 15 (64)     | 23.4 % | 0 (9)    | 0 %   |  |  |  |

|                                                                                                                              | LWF     | 3 (19)         | 15.5 % | 0 (24)      | 0 %    | 0 (4)    | 0 %   |  |  |  |

|                                                                                                                              | Tseng   | 6 (20)         | 30.0 % | 6 (39)      | 15.4 % | 0 (9)    | 0 %   |  |  |  |

| 14                                                                                                                           | JWF     | 117 (153)      | 76.5 % | 249 (405)   | 61.5 % | 0 (9)    | 0 %   |  |  |  |

|                                                                                                                              | MPEG    | 32 (651)       | 4.90 % | 256 (2,138) | 12.0 % | 0 (100)  | 0 %   |  |  |  |

| <ul> <li>For JWF, a large number of RTL paths are identified as CUPs</li> <li>The CPU time is less than 1 second.</li> </ul> |         |                |        |             |        |          |       |  |  |  |

| Evaluation for gate-level paths : Data-path          |           |             |               |        |  |  |  |  |

|------------------------------------------------------|-----------|-------------|---------------|--------|--|--|--|--|

| The number of gate-level paths corresponding to CUPs |           |             |               |        |  |  |  |  |

|                                                      | # CUPs    | #Gate-level | #Gate-level   | Ratio  |  |  |  |  |

| Circuit                                              | at RTL    | paths (CUP) | paths (total) |        |  |  |  |  |

| Paulin                                               | 12 (29)   | 65,430      | 117,576       | 55.7 % |  |  |  |  |

| LWF                                                  | 3 (19)    | 536         | 2,766         | 19.3 % |  |  |  |  |

| Tseng                                                | 6 (20)    | 7,978       | 16,532        | 48.3 % |  |  |  |  |

| JWF                                                  | 117 (153) | 20,972      | 26,000        | 80.7 % |  |  |  |  |

|                                                      |           |             | -             |        |  |  |  |  |

• For Paulin, Tseng and JWF, 50% - 80% paths are identified as false paths within 1 second.

• If we try to identify false paths at gate-level, for Paulin, the CPU time for only 100 paths takes 498 sec

## Conclusion

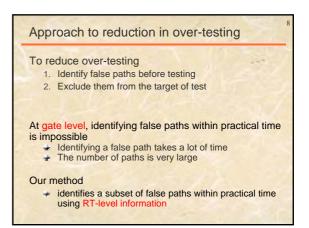

We proposed the method to identify a subset of false paths at RTL (control-dependent untestable paths) which

18

- ✤ can identify false paths within practical time, and (Dramatically reduce the CPU time)

- a can reduce over-testing

Our future work

Identifying not only control-dependent but also datadependent untestable paths at RT-level