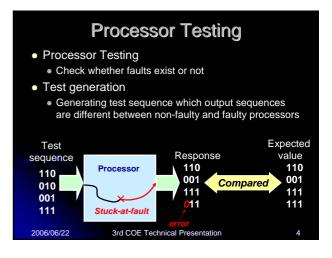

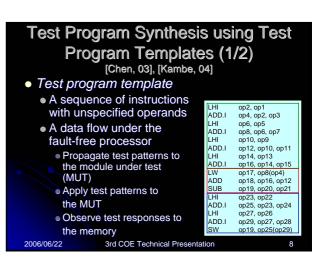

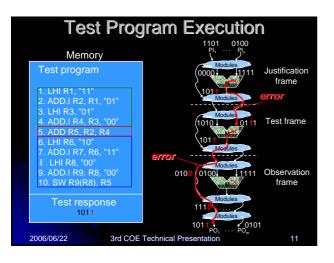

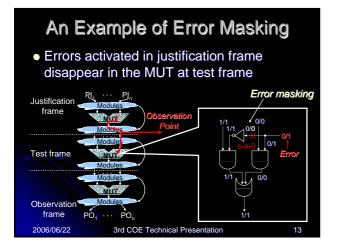

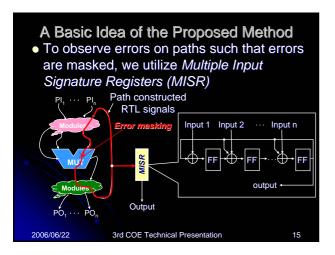

## When synthesizing the test program, the behavior under the faulty processor is not taken into consideration The behavior under the faulty processor is different from that under the fault-free processor Justifying test patterns and observing test responses are not guaranteed Error masking Some faults detected in the MUT test generation may not be detected by the test program synthesized from the test

## The Proposed Method

- We propose design for testability method which resolve error masking

- Add a function to initialize the value of all the registers

- Add a function to observe some RTL signals

- Advantages

- No delay overhead

- At-speed testing

2006/06/22 3rd COE Technical Presentation

14

## **Experimental Results** SAYEH Non-pipelined processor Dlx N Pipelined processor with 5 pipeline-stages Processor Area of DFT #OB HOH (%) original 165 full-scan 11.99 SAYEH 165 12389 Prop. method 106 25.28 full-scan 1379 23.23 DIX N 1379 58696 Prop. method 268 13.24 HOH: Hardware Over Head DFT: Design for Testability Observable bit 2006/06/22 3rd COE Technical Presentation 16

## Conclusion We propose design for testability of software-based self-test for processors Add a function to initialize the value of all the registers Add a function to observe some RTL signals Advantages Completely resolve error masking No delay overhead At-speed testing