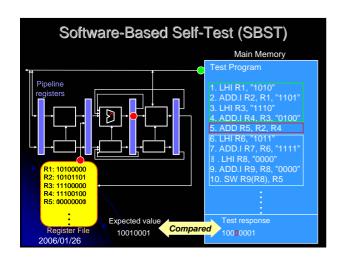

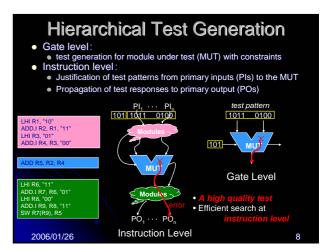

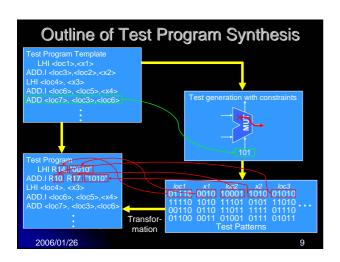

## The Proposed Method Efficient test program generation for Software-Based Self-Test of pipeline processors Generating the test program based on the hierarchical test generation Advantages A high quality test No hardware and delay overhead No extra power consumption for test

Find instruction sequence to propagate the results of the test instructions to main memory

## **Experimental Results**

- We utilize a pipeline version of DLX processor

- Target modules : ALU and FU

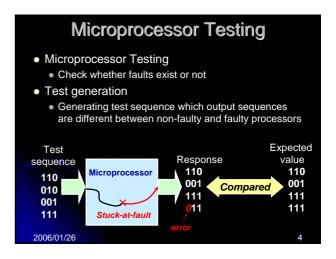

- Target fault : Single stuck-at-fault

| Module | # Faults | # Test program templates | Fault<br>efficiency (%) |

|--------|----------|--------------------------|-------------------------|

| ALU    | 8546     | 11                       | 98.81                   |

| FU     | 838      | 102                      | 83.65                   |

The proposed method achieved high fault efficiency for ALU and FU

2006/01/26

## **Conclusion and Future Work**

- Conclusion :

- We proposed the efficient test program generation for Software-Based Self-Test (SBST) of pipeline processors

- Generating a high quality test based on the hierarchical test generation

- Future Works :

- We consider Design for Testability for SBST in order to further improve the fault efficiency

2006/01/26