## **Research objectives**

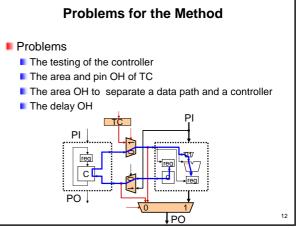

## Objectives

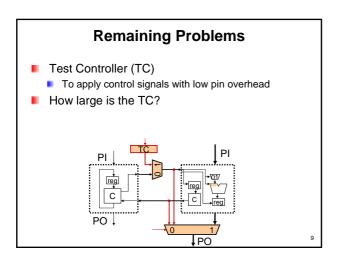

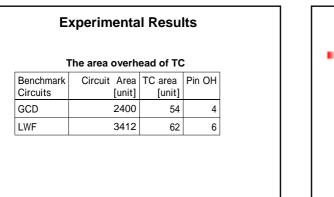

- To reduce the hardware overhead of TC

- To reduce the delay overhead

- To test the controller

- Target Circuits

- The whole RTL circuits

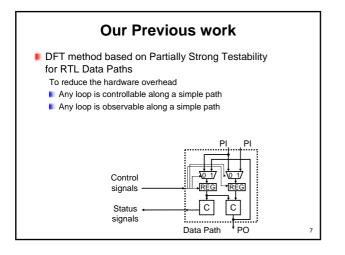

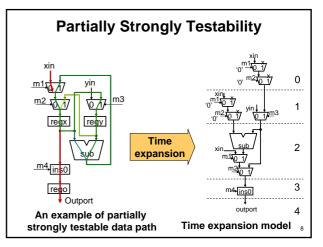

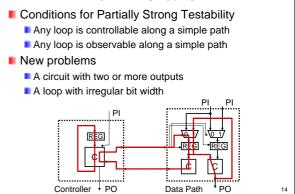

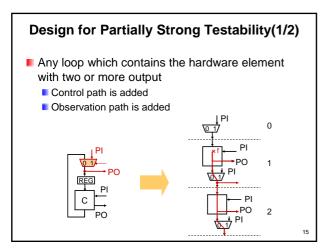

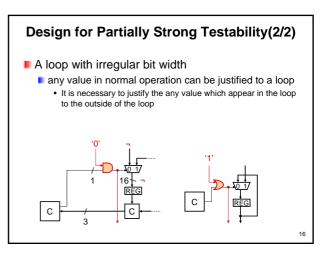

- Partially strong testability

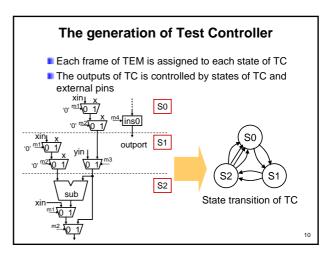

- The number of TEM is depended on the sequential depth of a simple path from PI to PO

13

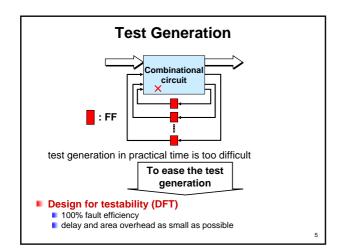

Combinational ATPG is applicable

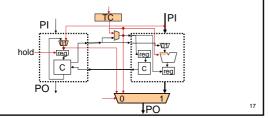

## Partially Strong Testability for RTL Circuits

- Every loop on the RTL circuit is controllable and observable

- The control signals which TC controls are reduced

- The signals which has the necessity for observation by PO are reduced