# A Design for 2-Pattern Testability of System-on-Chip Interconnects

Yusuke Saga Computer Design and Test Lab. (Fujiwara Lab.)

# Outline

- Research Background

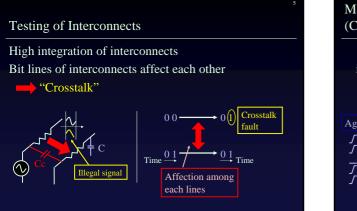

- Testing of Interconnects

- Design for 2-Pattern Testability

- Related Works

- Serial 2-Pattern DFT

- Parallel 2-Pattern DFT

- Case Study

- Conclusion

## Testing of SoC

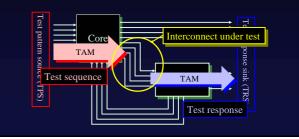

SoC: Cores and interconnects Testing by test access mechanism (TAM)

# Design for 2-Pattern Testability (1/2)

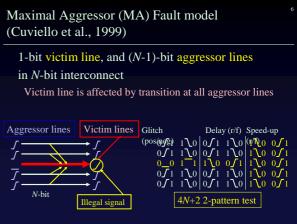

## 2-pattern testability

- 2-pattern controllability: capability to apply arbitrary two patterns consecutively

- 1-pattern observability: capability to observe arbitrary one response

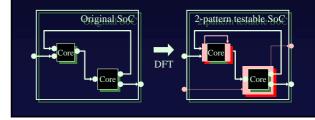

# Design for 2-Pattern Testability (2/2)

Design for testability (DFT)

- Design a circuit to be tested easily (testability) by adding extra hardware

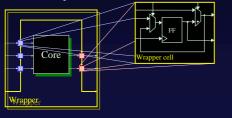

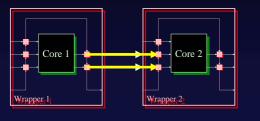

### Related Works (1) - IEEE P1500 Wrappers

#### Architecture for SoC testing by IEEE

- INTEST: Test mode for cores

- EXTEST: Test mode for interconnects

- BYPASS: Transparent mode for test of other cores

### Testing of Interconnects by EXTEST

- 1. Scan test pattern into wrapper output cells

- 2. Apply test pattern to interconnects

- 3. Scan test response out from wrapper input cells

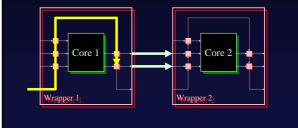

## Testing of Interconnects by EXTEST

- 1. Scan test pattern into wrapper output cells

- 2. Apply test pattern to interconnects

- 3. Scan test response out from wrapper input cells

#### Testing of Interconnects by EXTEST

- 1. Scan test pattern into wrapper output cells

- 2. Apply test pattern to interconnects

- 3. Scan test response out from wrapper input cells

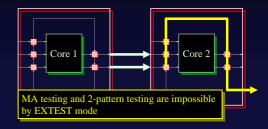

# Related Works (2) - Design for Consecutive Testability (Yoneda et al., 2002)

## Consecutive testability

- Consecutive controllability: capability to apply an arbitrary input sequence consecutively

- Consecutive observability: capability to observe an arbitrary response sequence consecutively

Testing of interconnects requires only two patterns

Area overhead can be reduced

# Objective of Our Work

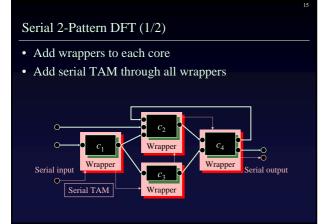

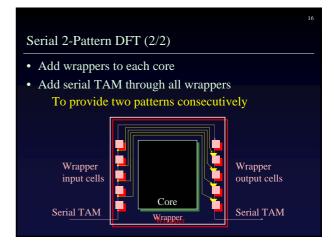

We proposed two DFT methods for 2-pattern testability of interconnects

• Serial 2-pattern DFT - DFT with serial TAM

#### Serial 2-Pattern DFT Problem Input: An SoC Output: A serial TAM and wrappers that make all interconnects 2-pattern testable Objective: Minimizing hardware overhead (No. of registers and MUXs, and area of additional lines) 0 $c_4$ $\mathcal{C}_1$ Wrapper Wrapper Wrapper Serial input Serial output $C_3$ C Serial TAM Wrapper

# Serial 2-Pattern DFT Algorithm

- 1. Design of wrapper for each core

- 2. Optimal design of a serial TAM that makes all interconnects 2-pattern testable

18

# Parallel 2-Pattern DFT (1/3)

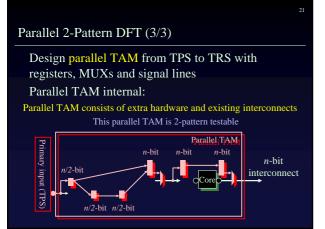

Design parallel TAM from TPS to TRS with registers, MUXs and signal lines

## Parallel 2-Pattern DFT (2/3)

Design parallel TAM from TPS to TRS with registers, MUXs and signal lines Parallel TAM internal: Parallel TAM consists of extra hardware and existing interconnects This parallel TAM is not 2-pattern testable

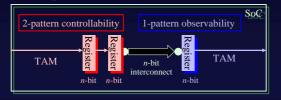

#### Parallel 2-Pattern DFT Problem An SoC Input: Output: A parallel TAM that makes all interconnects 2-pattern testable Objective: Minimizing hardware overhead (No. of registers and MUXs, and area of additional lines) *n*-bit n-bit *n*-bit 'rimary input (TPS)*n*-bit interconnect 2-pattern controllability 1-pattern observability

# Parallel 2-Pattern DFT Algorithm

- 1. Optimal design of a parallel TAM that makes all interconnects 2-pattern controllable

- 2. Optimal augmentation of the parallel TAM that makes all interconnects 1-pattern observable

#### 2

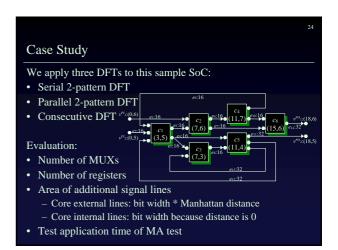

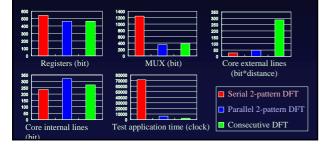

# Case Study Results

Serial 2-pattern DFT: Long test application time, large hardware area Parallel 2-pattern DFT: Short test application time, small hardware area

# Conclusion

We proposed designs for 2-pattern testability of interconnects

#### Serial 2-pattern DFT

• Large hardware and long test application time

# Parallel 2-pattern DFT

• Small hardware and short test application time than both serial 2-pattern DFT and consecutive DFT

Parallel 2-pattern DFT is effective method